- 基于FPGA的多傳感器管道內漏磁檢測系統

- 來源:賽斯維傳感器網 發表于 2014/12/2

摘要:

針對傳統管道漏磁檢測器檢測精度的不足,提出了新式的基于FPGA的高精度管道漏磁檢測系統設計,以適應813 mm管徑的管道檢測任務。主要介紹了系統邏輯設計,實現了多達400路傳感器漏磁 檢測信號的采集與存儲。該設計融合了多種總線協議,可有效解決管道漏磁檢測中的采集速率、功耗和精 度的問題。經實驗驗證,方案切實可行,為設計高精度管道漏磁檢測系統提供了新的解決方案。

關鍵詞:漏磁檢測;現場可編程門陣列;SPI總線;LVDS串行收發器;

0 引言

鐵磁性油氣輸送管道在長期使用后會因內外因素而造 成管壁腐蝕。腐蝕導致管道的輸送安全系數日益降低,如 果缺陷處出現泄露不及時處理,極其可能出現嚴重的后果, 對管道的安全運行造成潛在的危機。管道內漏磁檢測技術是利用漏磁檢測原理,使用霍爾傳感器檢測磁化后的管道,達到缺陷檢測的目的。目前,傳 統管道漏磁檢測器對于缺陷的探測、描述、定位及確定大小 的可靠性仍不穩定,不精確,需要改進的余地很大2。這 是因為傳統的管道內檢測器傳感器數量較少,無法進行高 精度的缺陷檢測,系統中傳感器數據采集存儲是依次進行的,一方面效率低,可靠性低,另一方面,功耗大,系統無法 進行長距離檢測。

本文針對這些問題,采用多級的現場可編程門陣列(FPGA),利用其高速的并行處理能力,靈活可變的現場可 編程能力以及豐富的IP核資源,實現400只霍爾型傳感器同時采集數據并及時存儲,滿足了高精度管道內漏磁檢測器的所需精度要求。

1 系統概述

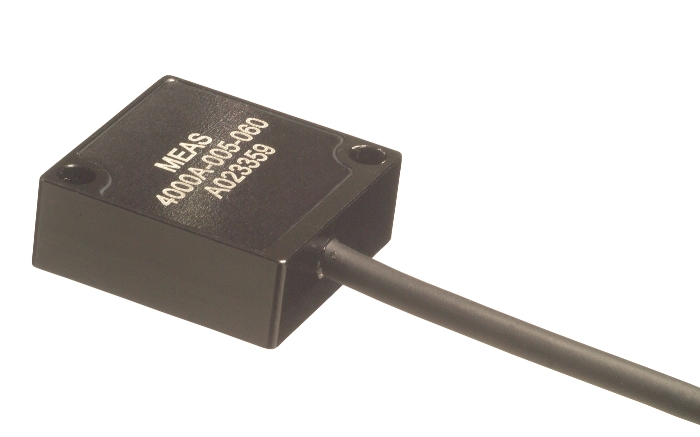

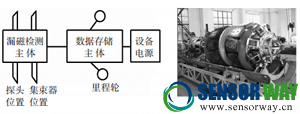

根據本系統設計的管道漏磁檢測器外部為圓柱形結 構,可以分為漏磁檢測、數據存儲和設備電源3個部分,結構示意圖如圖1所示。漏磁檢測主體外的圓周上均勻布置了5個集束器和80個檢測探頭,每個探頭包含不同擺放方 向的5只霍爾傳感器和控制采集的單片機,即共有400只 霍爾傳感器同時進行信號采集,以獲得高精度的管道檢測數據;主控FPGA的PCI板卡與PC104-PLUS板卡作為數據 存儲主體,確保大量傳感器數據的傳輸與存儲,后端為設備 電源部分;在數據存儲主體部分的兩側安裝有里程輪,用于記錄內檢測器走過的距離,并在運行中發送方波信號提示系統采集數據。

圖1管道內檢測器系統結構圖與實物圖

2 系統硬件組成

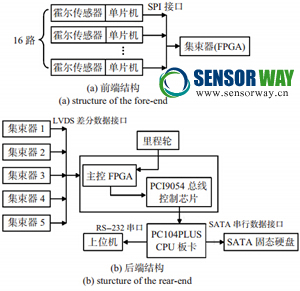

系統硬件組成可分為前端和后端兩大部分,如圖2所。

圖2 系統前端與后端硬件結構圖

圖2 (a)為前端數據采集結構,傳感器采用可休眠線性 霍爾型傳感器,具有5mV/Gs的

檢測精度,由單片機控制探 頭內5只傳感器電壓信號的A/D轉換,轉換精度為8位。集束器端FPGA選用Altera的Cyclonelll系列FPGA,主要 控制單片機的SPI傳輸和后端的LVDS串行傳輸。

圖2 (a)為后端數據存儲結構,PCI9054總線控制芯片 作為主控FPGA到PC104的總線控制器,使得PC104可以 直接通過PCI方式讀取主控FPGA內部緩存數據。主控FPGA 選

用 ALTERA 公司的 Stratix 的 EP1S20F484I6 型芯 片,具有20k的LE邏輯資源,主控邏輯設計LE單元使用率達75% ;內部靜態RAM大小為1.67 Mbit,可實現8位地址總線,32位并行數據總線的雙緩存乒乓設計,以滿足大量 數據的緩存要求。

3 系統邏輯設計

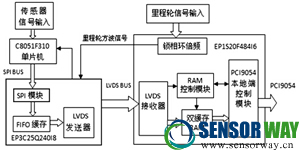

3.1總體邏輯設計

系統總體邏輯設計框圖如圖3所示。系統運行過程中,里程輪會隨著檢測器運行的距離變化發出周期性的方 波信號,主控FPGA通過倍頻的方式使其滿足設計要求的 采樣頻率,并行發送至前端數據采集系統,確保前端各單片 機同時進行A/D轉換。探頭內由單片機負責依次A/D轉 換5只霍爾傳感器感應到的磁通信號,通過SPI總線將采 集到的數據發送回集束器端的FPGA;5組集束器端的FP-GA通過LVDS串行收發器同時將前端數據發送到主控FP-GA,當主控FPGA內部緩存滿后,發送使能信號到PCI9054 橋芯片,通知PC104工控機讀取FPGA的內部緩存數據,并 將數據及時存儲到固態硬盤設備中。

圖3系統邏輯框圖

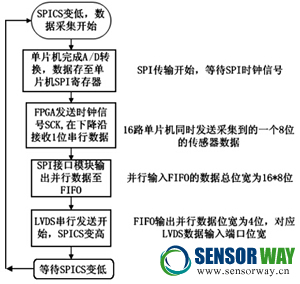

3.2SPI總線接口模塊與FIFO緩存模塊

集束器端FPGA作為SPI總線傳輸的主機端,提供2 MHz的SPI時鐘信號,16路單片機做為從機端,同時接收 SPI時鐘信號并發送數據。基于本系統龐大的前端傳感器 數量與單向的數據傳輸結構,只采用了主機輸入/從機輸出 數據線MISO, SPI時鐘線SCK和使能信號線SPICS 3的三 線形式即可完成SPI傳輸。SPICS信號默認為高電平,會根 據里程輪方波信號翻轉變為低電平,單片機接收到低電平 后開始A/D轉換數據和SPI傳輸,在單次SPI數據傳輸中 SPICS始終保持低電平狀態。通過設置異FIFO緩存模塊 讀寫時鐘和進出數據位寬,可協調SPI接收模塊與鐘和進出數據位寬,可協調SPI接收模塊與LVDS發 送器數據不同位寬和數據傳輸頻率不同的問題,前端SPI 數據傳輸的流程如圖4所示。

3.3 LVDS差分串行收發器模塊

根據內檢測器結構設計,從集束器FPGA到主控FPGA 的信號走線距離為4~5m,這種長度的走線一方面對較高頻率的數據傳輸信號衰減比較嚴重,另一方面會增加信號干擾,降低信噪比,嚴重會導致數據接收出錯。因此,采用 差分信號進行兩級FPGA之間的數據傳輸,它與普通單端 信號走線相比有3個明顯的優勢:抗干擾能力強、能有效抑制EMI、時序定位精確。

圖4 前端SPI數據傳輸流程圖

系統采用了 ALTERA公司提供的LVDS差分串行收發 器IP核,方便快捷地實現了差分串行數據傳輸:通過配置 LVDS發送器的端口位寬、通道數及傳輸速度,集束器端FPGA可將FIFO緩存輸出的并行4位數據轉為串行數據發送到主控FPGA,主控FPGA通過LVDS接收器將串行數據 解串為并行數據存入內部緩存中。串行收發器經實際測試 可達400 Mbps,遠遠滿足系統數據傳輸速度要求。

4 漏磁檢測數據分析

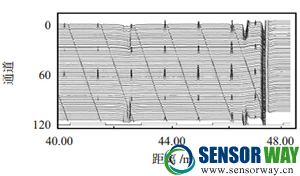

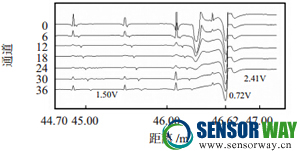

將管道內漏磁檢測系統置于813 mm管徑的直線測試 管道中進行牽引實驗,管道總長118 m,運行平均速度為 1.2m/s,經上位機軟件分析得出的各通道傳感器數據如 圖5,圖6所示。

圖5管道內漏磁檢測原始數據圖

圖6 管道44.70~47.00m段7通道傳感器數據分析圖

圖5為通過軟件分析得出的40.00~48.00m的其中120路管道漏磁檢測原始數據圖,橫軸

表示檢測器運行距 離,豎軸從上至下為均勻分布在管道檢測器外部圓周上的 各通道傳感器漏磁數據,圖下方為記錄距離的里程輪方波信號。

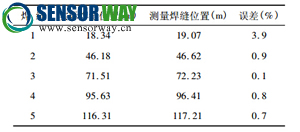

圖6表示圖5其中一段44.70~47.00m處管道的7個通道傳感器數據圖,管壁無缺陷處的電壓值為1.5V,變化 范圍為0~3V之間,46.62m處各路傳感器信號電壓值同時 下降到0.72V左右的位置應為管道該段的環焊縫所在位置。管道實際焊縫位置與系統測量得出的位置對比結果如 表1所示。

表1管道焊縫位置測量結果

從對比結果可知,測量出的管道焊縫位置與實際焊縫 位置基本一致,且通過分析各通道傳感器電信號變化的長 度幅度,可如實反映出實際管壁上缺陷的大小深度,說明系 統數據傳輸存儲穩定可靠,可實際應用于813 mm的大管徑 管道的檢測任務。

5 結論

本系統使用的Stratix系列的FPGA具有豐富的邏輯資 源,優秀的速度以及大容量的內部靜態RAM,實現了多達 400路漏磁傳感器信號的并行采集和快速存儲,通過FPGA 的功耗分析工具優化系統邏輯設計,可使系統整體功耗低 于75W,與傳統管道內漏磁檢測系統相比大大降低了功耗, 使系統適應長距離的管道檢測,實驗結果充分證明了系統 數據傳輸的準確性,為管道檢測及其他需求多傳感器數據 采集存儲的工程領域提供了一個值得借鑒的設計方案。(作者:尚林\李一博\陳世利\劉棟)

轉載請注明來源:賽斯維傳感器網(www.sensorway.cn)